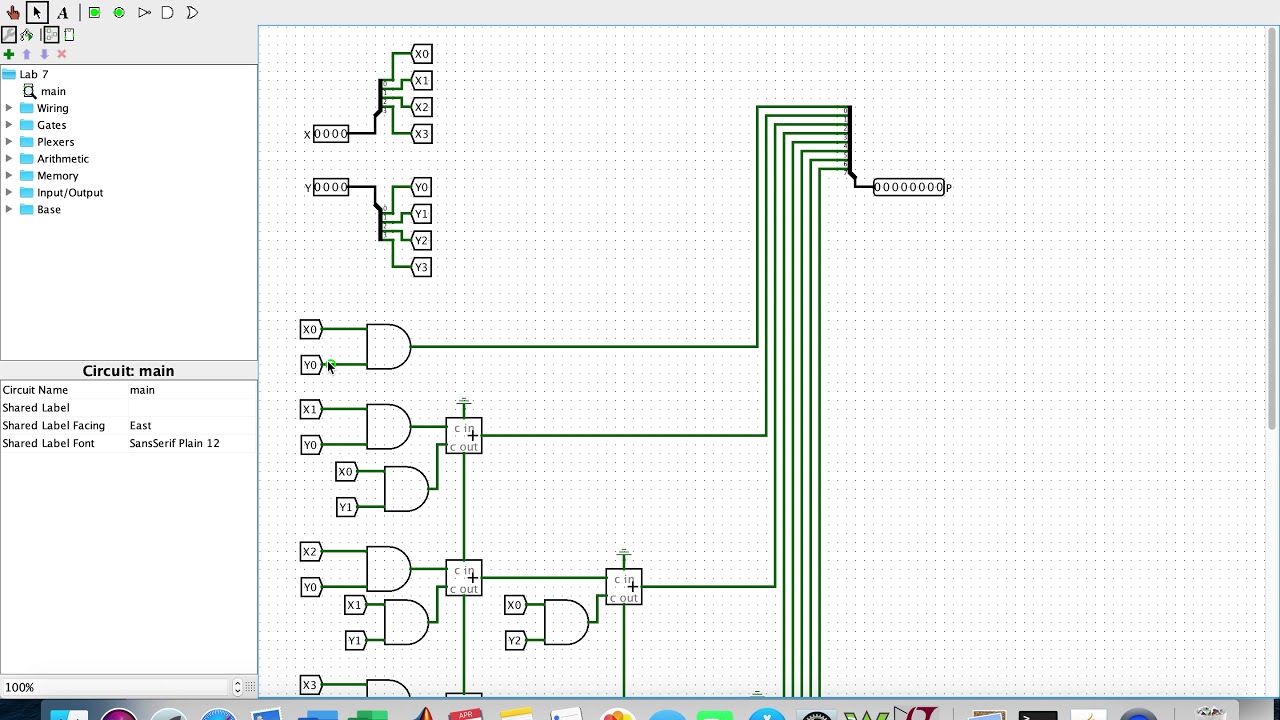

4 Bit Signed Multiplier

Multiplier wooley baugh verilog hdl Signed array multiplier Baugh multiplier wooley wooly logic reversible scirp

4-bit signed multiplier | Download Scientific Diagram

Traditional 4 bit array multiplier. 4-bit multiplier on logisim Multiplier bits

Multiplier verilog adders functional

Solved write the verilog module to describe the 4 x 34-bit multiplier Multiplier arrayMultiplier bit.

Four bit multiplier design.Multiplier signed Parallel integer multiplier (4x4 bits)Solved create a 4 bit signed multiplier with the following.

Solved: chapter 4 problem 20p solution

Multiplier circuit adder logic binary physics forumsLogisim multiplier bit Multiplier verilog complementDesign of compact baugh-wooley multiplier using reversible logic.

4 bit binary multiplier circuit diagramFigure 3 from design of baugh-wooley multiplier using verilog hdl Multiplier 4x4 integer array parallel bits gate levelSolved verilog code for the following diagram. [4 bit by 4.

4-bit signed multiplier

Multiplier bit four binary multiplies two unsigned adder numbers 20p diagram solved problem chapter .

.

Solved: Chapter 4 Problem 20P Solution | Digital Design 6th Edition

4 Bit Binary Multiplier Circuit Diagram - Wiring View and Schematics

Four bit multiplier design. | Download Scientific Diagram

Solved Write the Verilog module to describe the 4 x 3 | Chegg.com

Figure 3 from Design of Baugh-wooley Multiplier using Verilog HDL

Parallel integer multiplier (4x4 bits)

Solved Create a 4 bit Signed Multiplier with the following | Chegg.com

4-bit Multiplier

Design of Compact Baugh-Wooley Multiplier Using Reversible Logic